# HOLE TRANSPORT PROPERTIES OF Si / Si $_{1-x}$ Ge $_x$ MODULATION-DOPED HETEROSTRUCTURES

Jiang Ruolian, Liu Jianlin, Zheng Youdou Department of Physics, Nanjing University, Nanjing 210008, P.R. China

Li Haifeng, Zheng Houzh

National Laboratory for Superlattices and Microstructures,

Beijing 100083, P. R. China

(Received 22 August 1994)

We report hole transport properties of p-type Si/Si<sub>1-x</sub>Ge<sub>x</sub> modulation—doped heterostructures grown with rapid thermal processing very low pressure chemical vapor deposition (RTP-VLP CVD) at temperatures ranging from 293K to 77K. Hole mobilities as high as 300  $\,\mathrm{cm^2V^{-1}s^{-1}}$  at 293K, and 8400  $\,\mathrm{cm^2V^{-1}s^{-1}}$  at 77K for x = 0.3, have been achieved. The effects of Ge content and the thickness of Si spacer layer on the hole mobility are studied.

#### 1. Introduction

It is well known that modulation doped Si / SiGe heterostructures have become increasingly important for the fabrication of high speed device applications such as the Si / SiGe modulation-doped field-effect device. High electron mobility n-type Si / SiGe modulation doped heterostructures and high hole mobility p-type Si / SiGe modulation-doped heterostructures have been reported [1-4]. In this paper, we present the transport properties of p-type Si/Si1-xGex modulation-dope heterosturctrues by RTP-VLP CVD in the temperature range from 293K to 77K, desired for device application. It was found that the hole mobility increased strongly with decreasing temperature. A high hole mobility, 8400 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, has been achieved for a sheet carrier concentration of 1.2 × 1013 cm-2 at 77K. The effects of Ge content and the thickness of Si spacer layer on the hole mobility are studied.

## 2. Experimental

The Si/Si<sub>1-x</sub>Ge<sub>x</sub> P-type modulation-doped

(MD) heterostructures were grown with different x (x=0.2, 0.25, 0.3) values on (100) silicon wafers by RTP-VLP CVD. Details of the growth system have been reported earlier [5]. The heating source is a tungsten -hologen lamp which is used as a "thermal switch" to turn the CVD reaction on and off. SiH<sub>4</sub>, GeH<sub>4</sub> and B<sub>2</sub>H<sub>6</sub> are used as reactive gases and doping gases, respectively. All process parameters and sequences are controlled by computer. The operating pressure is  $10^{-3} \sim 10^{-2}$  torr, and the growth temperature was 600°C. The growth rate was as low as 0.1nm / sec.

Prior to growth, the Si wafers were cleaned by the RCA process [6], followed by a dilute HF dip which resulted in a H-terminated surface.

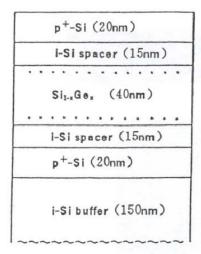

Fig.1 shows the schematic for a Si / Si<sub>1-x</sub>Ge<sub>x</sub> / Si p—type modulation—doped double heterostructure. P<sup>+</sup>–Si doping layers of 20nm thickness were doped with boron to  $1-3\times10^{19} {\rm cm}^{-3}$ , and Si<sub>1-x</sub>Ge<sub>x</sub> strained layers of 40nm thickness were not intentionally doped. The thickness of undoped Si spacer layer is 15nm.

For comparison, uniformly doped (UD) Si/

Fig. 1. Schematic for Si/Si<sub>1-x</sub>Ge<sub>x</sub>/Si p-type modulation-doped double heterostructure

$\mathrm{Si}_{1-x}\mathrm{Ge}_x$  heterostructures were also grown under the same growth conditions. The  $\mathrm{Si}_{0.8}\mathrm{Ge}_{0.2}$  layers of 180nm thickness were doped with boron to  $1-3\times10^{19}\mathrm{cm}^{-3}$ .

## 3. Results

The electrical characterization was performed using Hall-Van der Pauw measurements in the range 293-77K, as desired for device applications. The mobility and sheet hole concentration values are shown in Table 1. It was found that the hole mobility of p-type modulation-doped Si/Si<sub>1-x</sub>Ge<sub>x</sub> heterostructures is higher than that of bulk silicon. For indentical sheet carrier concentration, at room temperature, these hole mobilities are more than six times larger than those

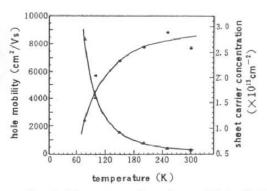

Fig. 2. Temperature dependence of hole Hall modility and sheet carrier concentration for Si / Si<sub>0.7</sub>Ge<sub>0.3</sub> / Si p-type modulation-doped double heterostructure

achievable in bulk doped Si. (See Table 1, sample No.5.) Low temperature hole mobility enhancement was observed in all MD samples. The peak hole mobility is 300 cm $^2$ V $^{-1}$ s $^{-1}$  at 293K and increases to 8400 cm $^{-2}$ V $^{-1}$ s $^{-1}$ at 77K for x = 0.3. The low temperature hole mobility of MD samples is much higher than that of UD sample No.4. This is evidence of carrier separation from parent impurities due to the valence band offset.

The hole mobility and sheet hole concentration as a function of temperature for a Si / Si $_{0.7}$ Ge $_{0.3}$ / Si MD heterostructure is shown in Fig.2. The hole mobility increases with decreasing temperature, because the lattice scattering decreases and the influence of remote ionized impurities scattering is very small. The decrease of sheet carrier concentration at low temperature indicates that some of the holes have been frozen out.

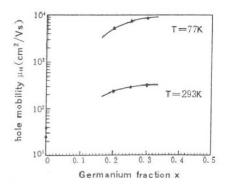

Fig.3 shows the dependence of hole mobility on Ge fraction x for MD heterostructures. Both at room

| Table 1. | Hall data fo | or MD and | UD samples at | 293K and 77K. |

|----------|--------------|-----------|---------------|---------------|

|----------|--------------|-----------|---------------|---------------|

| Sample |             | $P_1(\times 10^{13} \text{cm}^{-2})$ |                                     | $\mu_{\rm H}({\rm cm}^2/{\rm V\cdot s})$ |      |      |

|--------|-------------|--------------------------------------|-------------------------------------|------------------------------------------|------|------|

| No.    | Ge fraction | MD/UD                                | 293K                                | 77K                                      | 293K | 77K  |

| 1      | x = 0.2     | MD                                   | 6.6                                 | 2.2                                      | 240  | 5300 |

| 2      | x = 0.25    | MD                                   | 6.7                                 | 2.3                                      | 280  | 7500 |

| 3      | x = 0.3     | MD                                   | 2.6                                 | 1.2                                      | 300  | 8400 |

| 4      | x = 0.2     | UD                                   | 6.5                                 | 7.3                                      | 210  | 130  |

| 5      | x = 0       | UD                                   | $2.1 \times 10^{19} \text{cm}^{-3}$ | $3.1 \times 10^{19} \text{cm}^{-3}$      | 38   | 26   |

Fig. 3. Hole Hall Mobility VS Ge fraction at 293K and 77K for Si / Si<sub>1-x</sub>Ge<sub>x</sub> / Si p-type modulation -doped double heterostructure

temperature (293K) and low temperature (77K) the hole mobility increases with increasing x. The primary reason is that the hole effective mass decreases with the increment of Ge content, which is in agreement with the results of theoretical calculations [7].

In the design of sample structures, the thickness of spacer layers is very important, because the low temperature hole mobility is most probably limited by remote ionized impurity scattering from the  $p^+$ -Si layer and B segregation into the SiGe channel, as show in Fig.1. The effects of the thickness of the Si spacer layer on the hole mobility was studied. Our results show that a 15nm spacer layer thickness is optimal for producing maximum hole mobility in the range of 300-77K.

### 4. Summary

High hole mobility p-type  $Si/Si_{1-x}Ge_x$  modulation-doped heterostractures have been successfully

grown on silicon substrates by RTP-VLP CVD. The hole mobility was as high as 300 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at 297K, and 8400 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at 77K. It was found that the hole mobility is apparently enhanced by decreasing temperature, and also increases with increasing Ge content.

Acknowledgements — We greatly thank the 301 group of the Nanjing Electronic Devices Institute for Hall measurements, and the colleagues of our research group for their valuable discussion technical assistance.

#### REFERENCES

- Y.H.Xie, E. A. Fitzgerald, D. Monroe, P. J. Silverman, and G. P. Watson, J. Appl. Phys. 73, 8364 (1993).

- [2] F. Schäffler, D. Többen, H.J. Herzog, G. Abstreiter and B. Holländer, Semicond. Sci. Technol. 7, 260 (1992).

- [3] P.J. Wang, B.S. Meyerson, F. F. Fang, J. Nocera, and B. Parker, Appl. Phys. Lett. 55, 2333 (1989).

- [4] D.J.Gravesteijn, T. Mishima, C.W. Fredriksz, G.F.A. Van de Walle, and R.A. Van den Heuvel, J. of Crystal Growth, 111, 916 (1991).

- [5] Zheng Youdou, Zhang Rong, Jiang Ruolian, Hu Liqun, Zhong Perxing, Mo Shuiyuan, Yu Shidong, Li Qi, and Feng Duan, 20th International conference on the physics of semiconductors, Vol.2, p.869, Ed. by E. M. Anastassakis and J. D. Joannopoulos, world Scientific, Singapore, 1990.

- [6] K.Kern, Semicond. Int. 4, 194 (1984).

- [7] T. Manku and A. Nathan, IEEE Electron Device Letters. 12, 704 (1991).